FOWLP(Fan-Out Wafer Level Package)

マクセルのパッケージファウンドリは、FOWLP(Fan-Out Wafer Level Package)やWLCSP(Wafer Level Chip Size Package)といった、先端パッケージの少量多品種対応に特化したファウンドリサービスです。

半導体前工程技術とめっき技術を活用し、Cu再配線パッケージを作製。シリコン以外にも、SiCやGaNなど化合物半導体のパッケージ化も実績があります。

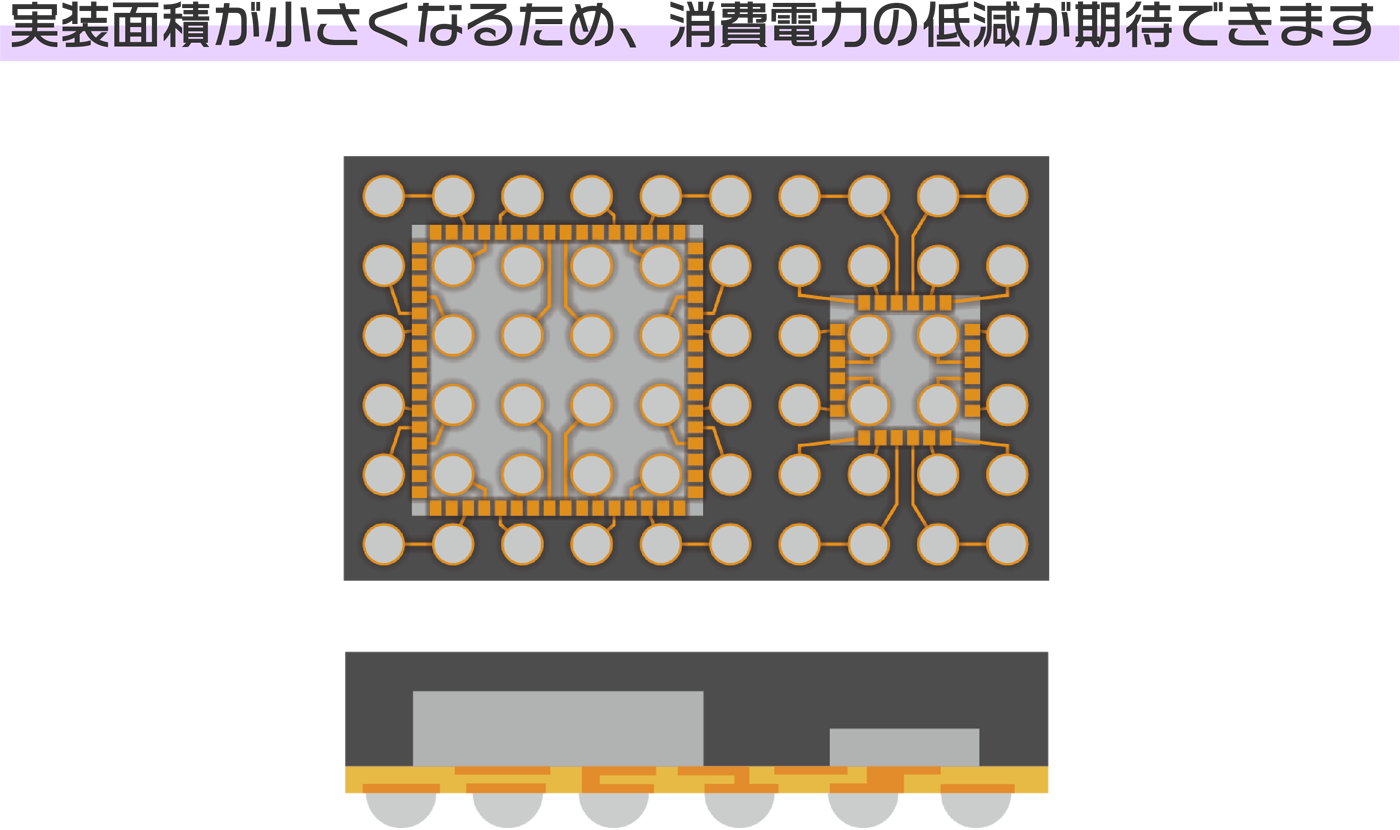

FOWLP(Fan-Out Wafer Level Package)構造は、パッケージ基板やワイヤーボンディング、はんだバンプを必要としないため、従来のFCBGA(Flip Chip Ball Grid Array)構造に比べ小型低背化が可能になります。

チップのAlパッド上にリソグラフィ技術とめっき技術による多層再配線を形成するため、従来のパッケージに比べ再配線設計の自由度が高いのも特長です。また、パッケージ厚min.100μmが可能です。

ウェハ状態で異種機能をチップ1個上にまとめて作製するより、機能ごとのチップを持ち寄り短距離で繋いでパッケージ(FOWLP)化することで、チップを作製する際の歩留り改善に貢献いたします。また、従来の個別の半導体パッケージで組み立てるより、機能ごとのチップ同士を近くに並べてめっき配線で繋ぐことで、チップ同士を繋ぐ配線長とモールド樹脂などの材料を半分以下に削減することができます。

∗ マクセル調べ

関連情報